ASML планира широко приложение на технологията High‑NA EUV още през следващата година за производство на чипове със размер на транзисторите от 1,4 nm и по-малки.

Кратко съдържание

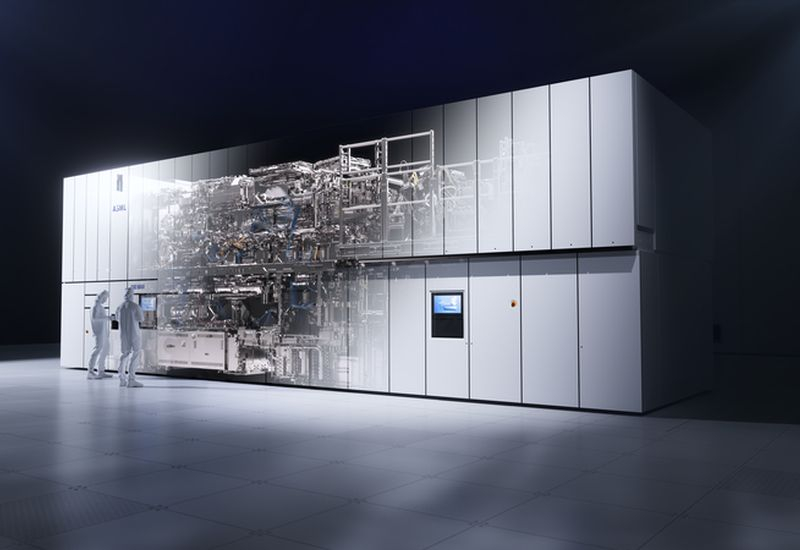

Новата фаза на миниатюризацията на микросхемите изисква преминаване към по-напреднали методи литография. През следващите два години индустрията трябва да стартира производство на чипове, използвайки оборудване от клас High‑NA EUV, което позволява достигане до размери до 8 нм за едно преминаване и отваря път към технологични процеси от 1,4 нм и по-малко от 10 нм (DRAM).

1. Технологичните възможности на High‑NA EUV

Параметър | Стойност

Числова апертура (NA) | 0,55

Минимален размер за едно преминаване | ≤ 8 нм

Възможни технологични процеси | 1,4 нм (интегрални микросхеми), < 10 нм (DRAM)

Тези характеристики правят оборудването ASML Twinscan EXE:5200B и подобните решения критично важни за бъдещите микроелектронни технологии.

2. Ключови играчи

Компания | Статус на внедряване | Коментар

ASML | Производител High‑NA EUV | Първите клиенти: Intel, Samsung, SK Hynix

TSMC | Не е готов за масово използване | Цената на една система – 380 млн USD; планира отказ от чипове 1,4 нм

Intel | В декември 2023 г. въведе Twinscan EXE:5200B | Подготовка за издаване на технология 14A и съпътстващо оборудване

Samsung Electronics | Получи първия скенер в декември 2023; вторият – в това полугодишие | Планира да го използва за Exynos 2600 (2 нм) и бъдещите Tesla‑процесори

SK Hynix | Осъществява High‑NA EUV от септември 2023 | Вече използва обичайна EUV литография в DRAM (10 нм), планира минимум пет слоя EUV за 6‑то поколение

Micron Technology | Все още не е определено кога ще внедри | Потенциални планове за High‑NA EUV

Rapidus (Япония) | Осъществява технология 2 нм; планира 1,4 нм през 2029 | Към 2027 г. трябва да стартира масово производство на 2‑нм чипове в Хоккайдо

3. Икономически аспекти

* Цената на оборудването – една система High‑NA EUV струва около 380 млн USD.

* Преминаването към по-скъпо оборудване увеличава себестойността на продукцията, което в крайна сметка се отразява върху потребителите.

* Затова големите производители (TSMC, Rapidus) проявяват предпазливост и планират внедряване постепенно.

4. Очаквани срокове

Нови литографични скенери ASML за масово производство на най-напреднала полупроводникова продукция ще започнат активно да се използват през 2027–2028 г. До тогава компаниите постепенно ще настройват своите производствени линии, интегрирайки High‑NA EUV в съществуващите технологични процеси.

Извод

Преминаването към High‑NA EUV е ключовата стъпка за достигане на размери до 1,4 нм и по-компактни DRAM. Най-големите световни играчи вече започнаха подготовителни работи, но масовото внедряване се очаква само след няколко години поради високите разходи и необходимостта от адаптиране на производствените вериги.

Asted Cloud

Asted Cloud

Коментари (0)

Споделете мнението си — моля, бъдете учтиви и по темата.

Влезте, за да коментирате